- 您现在的位置:买卖IC网 > Sheet目录368 > W631GG6KB-15 (Winbond Electronics)IC DDR3 SDRAM 1GBIT 96WBGA

�� �

�

�

�W631GG6KB�

�8.7�

�DLL� on/off� switching� procedure�

�DDR3� DLL-� off� mode� is� entered� by� setting� MR1� bit� A0� to� ―1‖;� this� will� disable� the� DLL� for� subsequent�

�operations� until� A0� bit� is� set� back� to� ―0‖.�

�8.7.1�

�DLL� “on”� to� DLL� “off”� Procedure�

�To� switch� from� DLL� ―on‖� to� DLL� ―off‖� requires� the� frequency� to� be� changed� during� Self� -Refresh,� as�

�outlined� in� the� following� procedure:�

�1.� Starting� from� Idle� state� (All� banks� pre-charged,� all� timings� fulfilled,� and� DRAMs� On-die� Termination�

�resistors,� R� TT� ,� must� be� in� high� impedance� state� before� MRS� to� MR1� to� disable� the� DLL.)�

�2.� Set� MR1� bit� A0� to� ―1‖� to� disable� the� DLL� .�

�3.� Wait� t� MOD� .�

�4.� Enter� Self� Refresh� Mode;� wait� until� (t� CKSRE� )� is� satisfied.�

�5.� Change� frequency,� in� guidance� with� section� 8.8� “� Input� clock� frequency� change� ”� on� page� 28.�

�6.� Wait� until� a� stable� clock� is� available� for� at� least� (t� CKSRX� )� at� DRAM� inputs.�

�7.� Starting� with� the� Self� Refresh� Exit� command,� CKE� must� continuously� be� registered� HIGH� until� all�

�t� MOD� timings� from� any� MRS� command� are� satisfied.� In� addition,� if� any� ODT� features� were� enabled�

�in� the� mode� registers� when� Self� Refresh� mode� was� entered,� the� ODT� signal� must� continuously� be�

�registered� LOW� until� all� t� MOD� timings� from� any� MRS� command� are� satisfied.� If� both� ODT� features�

�were� disabled� in� the� mode� registers� when� Self� Refresh� mode� was� entered,� ODT� signal� can� be�

�registered� LOW� or� HIGH.�

�8.� Wait� t� XS� ,� then� set� Mode� Registers� with� appropriate� values� (especially� an� update� of� CL,� CWL� and�

�WR� may� be� necessary.� A� ZQCL� command� may� also� be� issued� after� t� XS� ).�

�9.� Wait� for� t� MOD� ,� then� DRAM� is� ready� for� next� command.�

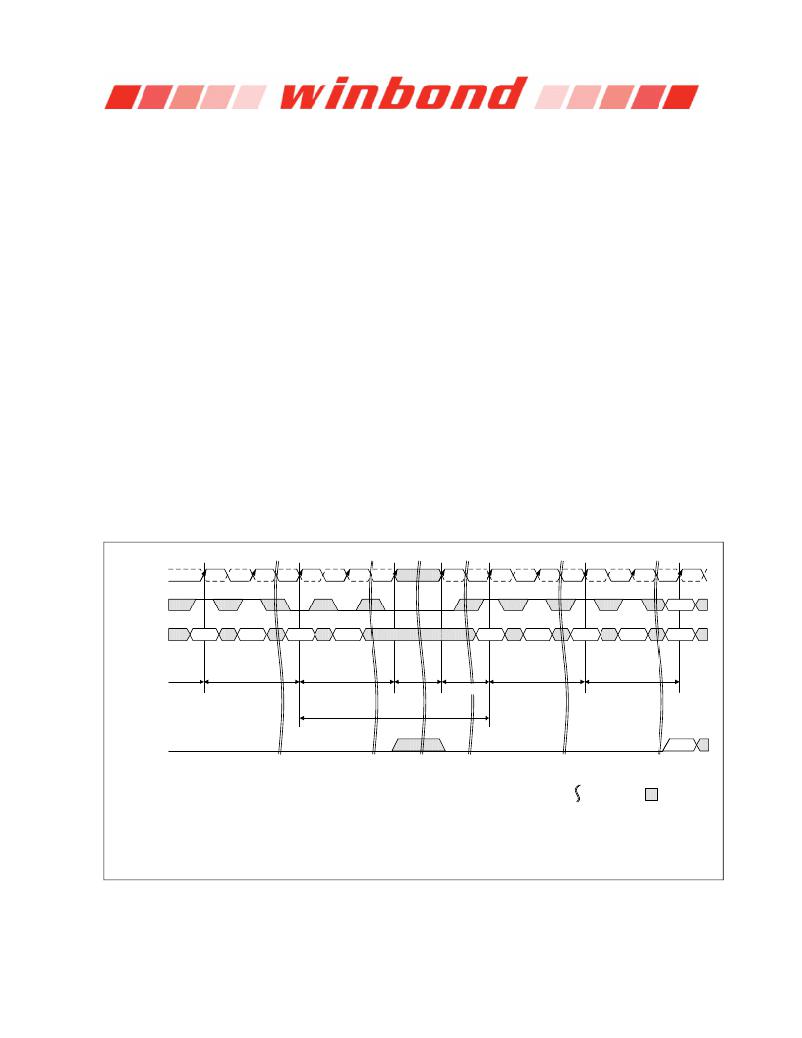

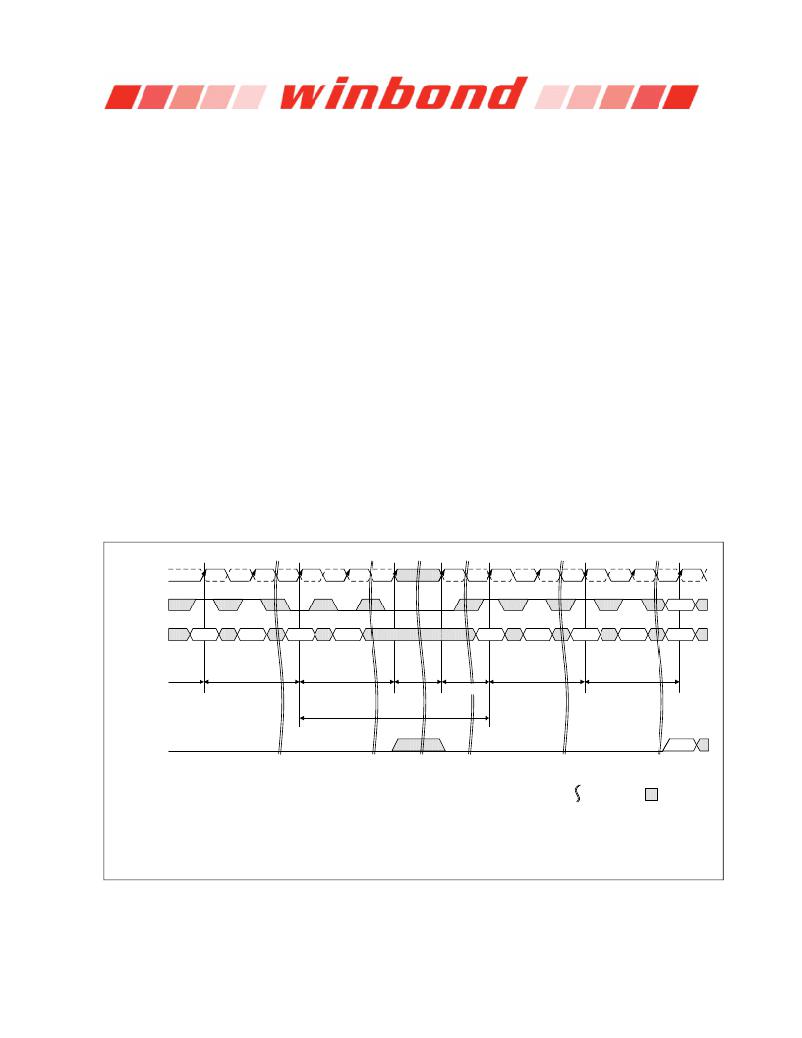

�T0�

�T1�

�Ta0�

�Ta1�

�Tb0�

�Tc0�

�Td0�

�Td1�

�Te0�

�Te1�

�Tf0�

�CK#�

�CK�

�CKE�

�VALID� *8�

�Command�

�MRS� *2�

�NOP�

�SRE� *3�

�NOP�

�SRX� *6�

�NOP�

�MRS� *7�

�NOP�

�VALID� *8�

�*1�

�t� MOD�

�t� CKSRE�

�*4�

�t� CKSRX� *5�

�t� XS�

�t� MOD�

�t� CKESR�

�ODT�

�Notes:�

�ODT:� Static� LOW� in� case� Rtt_Nom� and� Rtt_WR� is� enabled,� otherwise� static� Low� or� High�

�VALID� 8�

�1.� Starting� with� Idle� state,� R� TT� in� Hi-Z� state�

�2.� Disable� DLL� by� setting� MR1� Bit� A0� to� 1�

�TIME� BREAK�

�DON'T� CARE�

�3.� Enter� SR�

�4.� Change� Frequency�

�5.� Clock� must� be� stable� t� CKSRX�

�6.� Exit� SR�

�7.� Update� Mode� register� with� DLL� off� parameters� setting�

�8.� Any� valid� command�

�Figure� 10� –� DLL� Switch� Sequence� from� DLL-on� to� DLL-off�

�Publication� Release� Date:� Dec.� 09,� 2013�

�Revision� A05�

�-� 26� -�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

W9412G6IH-5

IC DDR-400 SDRAM 128MB 66TSSOPII

W9412G6JH-5I

IC DDR SDRAM 128MBIT 66TSOPII

W9425G6EH-5

IC DDR-400 SDRAM 256MB 66TSSOPII

W9425G6JH-5I

IC DDR SDRAM 256MBIT 66TSOPII

W947D2HBJX5E

IC LPDDR SDRAM 128MBIT 90VFBGA

W948D2FBJX5E

IC LPDDR SDRAM 256MBIT 90VFBGA

W949D2CBJX5E

IC LPDDR SDRAM 512MBIT 90VFBGA

W971GG6JB25I

IC DDR2 SDRAM 1GBIT 84WBGA

相关代理商/技术参数

W631GG8KB-11

制造商:Winbond Electronics Corp 功能描述:IC DDR3 SDRAM 1GBIT 制造商:Winbond Electronics Corp 功能描述:IC DDR3 SDRAM 1GBIT 78WBGA

W631GG8KB-12

制造商:Winbond Electronics Corp 功能描述:DRAM Chip DDR3 SDRAM 1G-Bit 128Mx8 1.5V 制造商:Winbond Electronics Corp 功能描述:IC DDR3 SDRAM 1GBIT 制造商:Winbond Electronics Corp 功能描述:IC DDR3 SDRAM 1GBIT 78WBGA

W631GG8KB-15

制造商:Winbond Electronics Corp 功能描述:IC DDR3 SDRAM 1GBIT 制造商:Winbond Electronics Corp 功能描述:IC DDR3 SDRAM 1GBIT 78WBGA

W632

制造商:LUMINIS 制造商全称:LUMINIS 功能描述:Wall mount

W632GG6KB-11

制造商:Winbond Electronics Corp 功能描述:IC DDR3 SDRAM 2GBIT 96WBGA

W632GG8KB-11

制造商:Winbond Electronics Corp 功能描述:IC DDR3 SDRAM 2GBIT 78WBGA

W634

制造商:LUMINIS 制造商全称:LUMINIS 功能描述:Wall mount

W638

制造商:LUMINIS 制造商全称:LUMINIS 功能描述:Wall mount